In Combinational circuits(Half adder, Full adder) post we have seen what are combinational circuits. In this post i am going to discuss about other two combinational circuits. They are

1)Half subs-tractor

2)Full subs-tractor

1)Half substractor :

It is a combinational circuit which is used to subs-tract two binary bits. In this circuit we have two inputs and two outputs. Let us consider the inputs as x and y and the outputs are D and B. Where D refers to different and B refers to borrower.

Truth table:

X Y D B

1)Half subs-tractor

2)Full subs-tractor

1)Half substractor :

It is a combinational circuit which is used to subs-tract two binary bits. In this circuit we have two inputs and two outputs. Let us consider the inputs as x and y and the outputs are D and B. Where D refers to different and B refers to borrower.

Truth table:

X Y D B

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

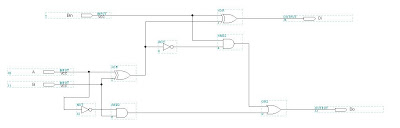

Diagram:

A full subs-tractor is a combinational circuit which is used for to subtract more than two binary bits. It is the combination o the half subs-tractors. It consists of more than two inputs and only two outputs.

Diagram:

Combinational circuits(Half adder, Full adder)

|

| Half |

subs-tractor

2)Full subs-tractor:A full subs-tractor is a combinational circuit which is used for to subtract more than two binary bits. It is the combination o the half subs-tractors. It consists of more than two inputs and only two outputs.

Let us consider the inputs are x,y,z and the outputs are D,B.

Truth table:

| X | Y | Z | D | B |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

|

| Full |

subs-tractor

Combinational circuits(Half adder, Full adder)